## **OMEGA** LOGIC ANALYZER

## **Reference Manual**

ASIX s.r.o. Na Popelce 38/17 150 00 Prague Czech Republic

www.asix.net

support@asix.net

sales@asix.net

ASIX s.r.o. reserves the right to make changes to this document, the latest version of which can be found on the Internet.

ASIX s.r.o. renounces responsibility for any damage caused by the use of ASIX s.r.o. products.

© Copyright by ASIX s.r.o.

## **Table of Contents**

| 1 General Information                             | 5  |

|---------------------------------------------------|----|

| 1.1 Product Overview                              | 5  |

| 1.2 Package Contents                              | 5  |

| 1.3 Panel Overview                                | 6  |

| 1.4 Product Version                               | 6  |

| 2 Getting started                                 | 7  |

| 2.1 Installation on Windows                       | 7  |

| 2.2 Target connection                             | 7  |

| 2.3 Acquire the data                              | 7  |

| 3 Controls                                        | 9  |

| 3.1 Indicators and button                         | 9  |

| 3.2 Target Connection                             | 9  |

| 4 Using SIGMA & OMEGA Logic<br>Analyzers Software | 11 |

| 4.1 Clock Source                                  | 11 |

| 4.1.1 Modes of operation                          | 11 |

| 4.1.2 Synchronous Clock Timing                    | 13 |

| 4.2 Input pins                                    | 13 |

| 4.3 Traces                                        | 13 |

| 4.4 Trigger Settings                              | 14 |

| 4.4.1 Basic Trigger Settings                      | 15 |

| 4.4.2 Advanced Trigger Settings                   | 15 |

| 4.4.3 Trigger Position within Acquisition         | 16 |

| 4.4.4 External Triggering                         | 17 |

| 4.4.5 Other Trigger Settings                      | 17 |

| 2    | 4.4.6 Amount of triggers                           | 1                      | 8 |

|------|----------------------------------------------------|------------------------|---|

| 4.5  | Working with the acquire                           | ed data 19             | 9 |

| 4    | 4.5.1 Navigation and analysis                      | 1                      | 9 |

| 2    | 4.5.2 UART Protocol Decoder                        | 2                      | 0 |

| 2    | 4.5.3 SPI Bus Decoder                              | 2                      | 1 |

| 2    | 4.5.4 I2C Bus decoder                              | 2                      | 1 |

| Z    | 4.5.5 1-Wire Bus decoder                           | 2                      | 2 |

| Z    | 4.5.6 USB 1.1 Analyzer Plugin                      | 2                      | 2 |

|      | Installation                                       | 2                      | 3 |

|      | What to measure                                    | 2                      | 3 |

|      | Measure tool attachment                            | 2                      | 3 |

|      | Measuring                                          | 2                      | 4 |

|      | Processing                                         | 2                      | 4 |

|      | Viewing                                            | 2                      | 4 |

|      | Searching                                          | 2                      | 5 |

|      | Linking the events window window                   | with the analyzer 2    | 6 |

|      | Gathering of related comm                          | unication into trees 2 | 6 |

| 4.6  | Auxiliary functions                                | 20                     | 6 |

| Z    | 4.6.1 Insider                                      | 2                      | 7 |

| 4    | 4.6.2 Function Generator                           | 2                      | 9 |

| 4.7  | Frequency Measuring                                | 30                     | 0 |

| 4.8  | Pin View                                           | 30                     | 0 |

| 4.9  | Availability of Auxiliary F                        | unctions 30            | 0 |

| 4.10 | Using the Application for<br>Acquisition           | r Automated 33         | 1 |

| 4.11 | Command Line Interface                             | e omegacli.exe 33      | 1 |

| 4.12 | Data streaming using Co<br>Interface omegartmcli.e |                        | 2 |

|      |                                                    |                        |   |

| 4.13 Conversion to and from binary data<br>stream using bin2stf.exe a stf2bin.exe | 32 |

|-----------------------------------------------------------------------------------|----|

| 4.14 Working with binary data stream using binconvert.exe                         | 33 |

| 4.15 Tips on working with binary data stream                                      | 33 |

| 4.16 Plugins                                                                      | 33 |

| 5 Using the Logic Analyzer                                                        | 35 |

| 5.1 Sampling Frequency                                                            | 35 |

| 5.2 Powering the Analyzer                                                         | 35 |

| 5.3 Using the Application as a Portable<br>Application                            | 36 |

| 6 Synchronization                                                                 | 38 |

| 6.1 Logic Analyzer Connection to PC when<br>Using Synchronization                 | 38 |

| 6.2 Synchronization Interconnection                                               | 38 |

| 6.2.1 Using Synchronization Cable                                                 | 38 |

| 6.2.2 Interconnection of two Logic Analyzers                                      | 39 |

| 6.2.3 Interconnection of three Logic Analyzers                                    | 39 |

| 6.2.4 Interconnection of more than three Logic Analyzers                          | 39 |

| 6.3 Synchronization Accuracy                                                      | 40 |

| 7 Using OMEGA Logic Analyzer under<br>Linux                                       | 41 |

| 8 OMEGA and SIGMA2 Comparison                                                     | 43 |

| 9 Specifications                                                                  | 44 |

| 10 Document history                                                               | 46 |

## **General Information**

### 1.1 Product Overview

OMEGA is a logic analyzer - development tool designated for tracing and debugging of TTL (and compatible) digital signals.

OMEGA Logic Analyzer is the highest performance logic analyzer by ASIX s.r.o. from series of SIGMA/SIGMA2/ OMEGA Logic Analyzers.

The OMEGA Logic Analyzer is equipped with 512 Mb of memory (equivalent to 64 MB) and provides with up to 16 digital inputs and sampling rate of 200 Msps by a single device. More inputs and memory can be utilized using synchronization between multiple logic analyzers units. Built-in data compression allows for tracing of long running signals without exhausting logic analyzer memory. When using all 16 inputs per analyzer, guaranteed minimum capacity is over 29 million samples<sup>1</sup> at full speed. OMEGA uses High-Speed USB 2.0 (480 Mbps) which ensures both data transfer and power delivery with a single cable. There is no additional power supply needed.

Features:

- Up to 16 TTL compatible inputs per unit

- Synchronization between multiple units

- Up to 400 Msps sampling rate (limited number of inputs)

- External clock up to 99.95 MHz

- 512 Mb of internal memory

- Real-Time mode utilizing the memory only as a FIFO buffer

- Advanced hardware scompression

- Flexible trigger options

- USB interface for data and power

## 1.2 Package Contents

Please inspect the logic analyzer mechanically and electrically upon receiving it. Unpack all items from the shipping box and check for any obvious signs of physical damage that may have occurred during transportation. Report any damage to the shipping agent immediately. We recommend to save the original packing carton for possible future reshipment. Every logic analyzer is shipped with the following contents:

- OMEGA Logic Analyzer

- Target cables:

- 20 individual pins (SIGMACAB)

- one-to-one 20 pins (SIGCAB20)

- one-to-one 10 pins (SIGCAB10)

- USB cable (A-B)

- Synchronization header

- Synchronization cable

- Optional accessory (must be ordered separately):

- Set of 10 variously colored hooks (PicoHook10)

Verify that all ordered items are included in the shipping container. If anything is missing, please contact your local distributor.

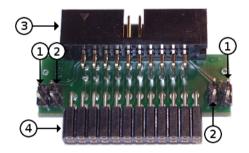

## 1.3 Panel Overview

Fig. 2: OMEGA Panel Overview

#### Panel Overview

| 1 | USB port                                |

|---|-----------------------------------------|

| 2 | Indication LEDs                         |

| 3 | Multifunction Start/Stop/Trigger button |

| 4 | Target interface                        |

## 1.4 Product Version

The logic analyzer may come in different hardware or software version. This manual reflects features and options of logic analyzer software equipment **Logic Analyzer version 3.00**. Updates to the latest version of the software are always available free of charge on the internet at www.asix.net. The main software comes with many supporting utilities, which may be different version.

| Trade Name | Serial Number     | Availability |                        |  |  |  |  |

|------------|-------------------|--------------|------------------------|--|--|--|--|

| SIGMA      | Since<br>A6010001 | Since 2007   | No longer<br>available |  |  |  |  |

| SIGMA 2    | Since<br>A6020001 | Since 2011   | Low cost               |  |  |  |  |

| OMEGA      | Since<br>A6030001 | Since 2012   | Flagship               |  |  |  |  |

Table 1: Logic Analyzer Versions

The logic analyzer software supports basic functionality of all logic analyzer hardware versions in the table, but advanced features availability may differ. This manual describes the hardware and software features available only to the OMEGA Logic Analyzer.

Detailed comparison of the logic analyzers is in the chapter OMEGA and SIGMA2 Comparison.

<sup>&</sup>lt;sup>1</sup> OMEGA will use approximately 18.1 bits of memory per 16 input sample.

## **Getting started**

Before connecting and powering up the logic analyzer, please review and go through all the instructions in this chapter. You will learn all basic functions required to debug your first application with the logic analyzer.

## 2.1 Installation on Windows

Install the ASIX SIGMA & OMEGA Application Package available at www.asix.net to your computer. Check the web page periodically for software updates. Software updates are free and may address discovered problems and add new features. The OMEGA Logic Analyzer is a USB device, therefore it requires USB drivers. The drivers are installed automatically during software package installation. Connect OMEGA to a USB port or a USB hub using supplied cable. In a while green ON-LINE LED should turn on and the OMEGA Logic Analyzer should appear in the Device manager as correctly installed.

## 2.2 Target connection

The OMEGA Logic Analyzer is equipped with 16 high impedance inputs with logic levels compatible to TTL and auxiliary *Trigger In* and *Trigger Out* pins.

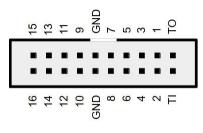

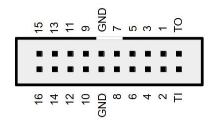

Fig. 3: Target connector

Always connect the ground between the application and the analyzer and then connect desired input pins. The OMEGA Logic Analyzer do not isolate ground between the PC and the application.

If you want to use *Trigger In* and *Trigger Out* pins, use **Settings**  $\rightarrow$  **Trigger Options...**, tab **Other Settings**.

Warning: Trigger In and Trigger Out pins are not 5V tolerant!

**Note:** Capacitance and length of the probe cables should be taken into consideration when connecting to a debugged application, otherwise a cross-talks of fast signals may occur. The leads of the supplied cable with individual pins may be split to reduce capacitance between adjacent wires for mid-range signal speeds. For high-speed signals, using of any cable is not recommended, it is recommended to connect directly the logic analyzer to the application.

## 2.3 Acquire the data

Start the application ASIX SIGMA & OMEGA Logic Analyzers from start menu and launch the data acquisition by pressing **Enter**. The OMEGA memory will last most probably for minutes, so you can stop data acquisition any time by pressing button *Stop Acquisition Now*.

To zoom, select a range with mouse or use key + or \* on keyboard.

- To take back last zoom operation, use key -, **Backspace** or /.

- To move over the measured data, use arrow keys →,

←, Page Down and Page Up, mouse wheel or hold

Ctrl key while moving mouse pointer.

- Using Alt+←/Alt+→ you can jump to next change on a line where the mouse pointer is.

- Jump to another line is possible with arrows  $\uparrow$  and  $\downarrow$ .

- To measure time or frequency or count number of edges, use keys **Spacebar**, **F** and **Q**.

- To select a trigger, press **T** key and to use different clocking options, press **C** key.

- OMEGA Logic Analyzer supports many auxiliary functions. You can setup them with **U** key (U for *utilities*).

| 2 700 | ) µз | і і і і і і<br>2 704 µs | '   '   '   '  <br>2 708 μs | '   '   '   '<br>2 712 μs | '   '   '  <br>2 716 µs                                   | 27 |

|-------|------|-------------------------|-----------------------------|---------------------------|-----------------------------------------------------------|----|

|       |      |                         |                             |                           | 16 rising edges<br>2 713 865 ns<br>13 240 ns<br>2 648 CLK |    |

Fig. 4: Counting edges in an acquisition

To start using protocol analyzers, double click any trace label on left margin of the window to add a new line. Every new protocol analyzer is on a separate line, called a *trace*.

## 3

## Controls

### 3.1 Indicators and button

Main panel contains two bi-color LED indicators providing an operator with quick status information.

#### ONLINE / BUSY (green/yellow LED)

OMEGA is in low-power (Sleep) mode or no USB driver has been installed (Windows only) or no synchronization signal is being received during Daisy-Chain operation

**green:** OMEGA is ready to operate

• **yellow:** OMEGA is acquiring data

#### TRIGGER STATUS (red/yellow LED)

- **off:** Trigger logic is inactive no trigger condition has been detected

- **red:** OMEGA is waiting for trigger condition

**yellow:** flashes when trigger condition or trigger pattern has been matched

The GO button helps to control the analyzer comfortably it cyclically switches among essential operation states. When it is pressed in idle state the data acquisition is launched. When it is pressed in running state the software trigger is initiated. When it is pressed in triggered state <sup>1</sup> the acquisition is stopped, idle mode is launched and the data transfer from logic analyzer memory to PC begins.

## 3.2 Target Connection

#### Fig. 5: Target connector

The OMEGA Logic Analyzer is equipped with sixteen high impedance inputs with TTL input logic levels and  $1 \text{ M}\Omega$  pull-down resistors to park the pins when they are unused. The functions *Trigger In* and *Trigger Out* are available. The function *Power Output*<sup>2</sup> is available on *Trigger In*. The function of Synchronization (Daisy-Chain connection) is available on the *Trigger In/Trigger Out* pair.

Warning: Trigger In and Trigger Out pins are not 5V tolerant!

If you want to use *Trigger In* and *Trigger Out* pins, use **Settings**  $\rightarrow$  **Trigger Options...**, tab **Other Settings**.

The digital inputs are organized as two 8-pin ports (inputs 1 to 8 are merged into port 1, inputs 9 to 16 are merged into port 2). Pin-to-pin skew between inputs on a single port is rather low while it may be considerably higher between the ports.

Always connect the ground between the application and the analyzer and then connect desired input pins. OMEGA Logic Analyzer do not isolate ground between the PC and the application <sup>3</sup>.

|                                                      | min. | typ. | max. |    |

|------------------------------------------------------|------|------|------|----|

| V <sub>IL</sub> input low voltage                    |      |      | 0.8  | V  |

| V <sub>IH</sub> input high voltage                   | 2.0  |      |      | V  |

| $V_{IN}$ absolute rating, inputs 116                 | -0.3 |      | 5.5  | V  |

| V <sub>IN</sub> absolute rating, trigger I/O         | -0.3 |      | 3.6  | V  |

| t <sub>sksp</sub> pin-to-pin skew within single port |      | 1    |      | ns |

| t <sub>skbp</sub> pin-to-pin skew between ports      |      | 4.8  |      | ns |

Table 2: Inputs Electrical Specifications

- **Note:** Capacitance and length of the probe cables should be taken into consideration when connecting to a debugged application, otherwise a cross-talks of fast signals may occur. The leads of the supplied cable with individual pins may be split to reduce capacitance between adjacent wires for mid-range signal speeds. For high-speed signals, using of any cable is not recommended, it is recommended to connect directly the logic analyzer to the application.

- <sup>1</sup> When using OMEGA Real-Time mode where is unconstrained number of triggers, end of acquisition can be performed by long pressing of the GO button.

- <sup>2</sup> Usage of any OMEGA-powered logic level translator is possible thanks to possibility to power it from the logic analyzer using *Power Output* feature on *Trigger In* pin.

- <sup>3</sup> When using a USB optoisolator designed for USB Full-Speed (12 Mbps) you will benefit from unique OMEGA feature: The logic analyzer will download the data you are currently looking at in preference. Therefore, the data you are looking at will be available virtually in the same time you will focus on them.

## Using SIGMA & OMEGA Logic Analyzers Software

## 4.1 Clock Source

### 4.1.1 Modes of operation

OMEGA can operate in one of several modes adapted to actual user needs and particular debugged application (number of inputs, sampling period etc...). The mode of operation can be selected in **Settings**  $\rightarrow$  **Clock source**.

| Clock Options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

| <ul> <li>Clock Source Setup</li> <li>Basic mode, 16 inputs, sampling rate 200 MHz</li> <li>Basic operation mode, sampling is derived from internal oscillator with accuracy 50 ppm. Lower sample rates are not necessary, because of RLE-based compression.</li> </ul>                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |  |  |

| Daisy chain, 16*n inputs, sampling rate 200 MHz<br>Several OMEGA Logic Analyzers connected together with synchronization cable.                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |  |  |  |  |

| Higher sampling rate, 8 inputs, sampling rate 400 MHz<br>Sampling rate is fixed at 400 MHz with reduced number of input pins to eight. Input pins Input 1 to<br>Input 8 are available, basic trigger options are available.                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |  |

| Real-Time Mode, 16 inputs, sampling rate 200 MHz, unlimited memory<br>Whole memory of OMEGA Logic Analyzer works as FIFO, directly streaming samples into PC.<br>Bandwidth is limited by USB 2.0 and acquisition length is limited by available memory in PC.                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |  |  |  |

| External synchronous dock source (up to 99 MHz) In this mode, input holding Filp-Flops are sampled directly by edge of the selected clock. This mode profits in very small setup and hold times. Full trigger options are available. Maximum safe operating frequency is 99 MHz. PLL or DLL is not used, thus clock-to-clock period can vary, but clock must remain continuous. Clock must be continuous and applied before test starts.     Sample data on rising edge     Sample data on falling edge     Asynchronous Time Scale |  |  |  |  |  |  |  |  |  |  |

| Synchronous Pins Delay Adjustment<br>Input pins delay class: 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |  |  |

| Typical Values     Max: Inputs 2 - 8     Max: Inputs 9 - 16       Setup     Hold     Setup     Hold       0.10 ns     1.10 ns     1.10 ns     4.90 ns     5.90 ns                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |  |

| QK <u>C</u> ancel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |  |  |

Fig. 6: Modes of operation

Available modes of operation:

#### **Basic Mode**

16 inputs, sampling rate 200 Msps. Basic operation mode, sampling is derived from internal oscillator.

#### **Daisy Chain Mode**

$16 \times n$  inputs, sampling rate 200 Msps. Several OMEGA Logic Analyzers connected together with a synchronization cable.

#### Higher Sampling Rate Mode

8 inputs, sampling rate 400 Msps.

Number of input pins is reduced to eight with benefit of twice sampling rate. Inputs are limited to single port due to higher demands on the delay skew between inputs.

#### **Real-Time Mode**

16 inputs, sampling rate 200 Msps.

The whole internal memory works as FIFO buffer and data are streamed in real-time to the PC. This mode is very memory demanding, therefore lot of free RAM and free space on hard drive is required.

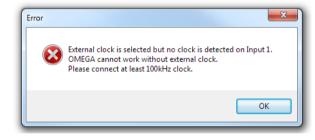

#### Synchronous Clock Mode

15 inputs, external clock.

Input1 is utilized as external clock input. Rising or falling sampling edge or both (DDR) can be chosen. Clock speed should be within the range of ~100 kHz to 99.95 MHz. Due to internal pipeline circuits. the clock signal must be present before start of the data acquisition and some time after the end of the acquisition otherwise several last samples will not be contained in the captured data. Using this mode for measuring synchronous bus (e.g. processor can be advantageous. bus) The synchronous clock can be used with or without asynchronous time information<sup>1</sup>.

### Synchronous clock Mode Without Asynchronous Time Scale

The OMEGA Logic Analyzer tries optionally to measure the clock speed with auxiliary low resolution frequency counter and uses this information for time scale. Because time information is not included in the acquisition data, the memory usage is lower compared to the mode with Asynchronous Time Scale enabled.

### Synchronous clock Mode With Asynchronous Time Scale

With external clock frequencies <40 MHz, The OMEGA Logic Analyzer can together with the data also save the time with resolution 10 ns. Higher frequencies up to the maximum possible external clock frequency are allowed, but the accuracy is degraded due to higher utilization of the clock synchronization circuitry. It is not possible to use both DDR and Asynchronous Time Scale at the same time.

Fig. 7: Clock not present on Input 1 during OMEGA Synchronous Clock Mode

The clock on Input 1 must be continuous and present before the acquisition starts.

**Note:** Data compression (RLE and Huffman coding) is used in every case, disregarding selected mode, giving possibility to capture long time running signals with precise timing. The actual compression ratio depends on characteristics of the particular signal.

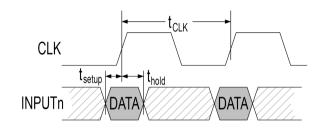

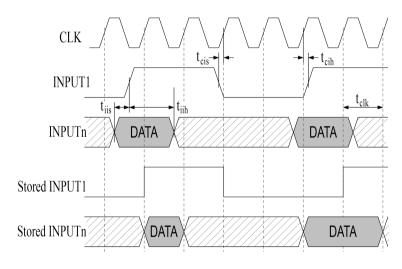

### 4.1.2 Synchronous Clock Timing

Fig. 8: Synchronous clock timing

The synchronous clock timings are measured at the input connector. At the maximum clock rates, use of custom cables and amplifiers may be necessary.

| Delay<br>Class | Тур                         | pical                     | Maxir<br>Inputs             |                           | Maxir<br>Inputs             |                           |    |

|----------------|-----------------------------|---------------------------|-----------------------------|---------------------------|-----------------------------|---------------------------|----|

|                | Setup<br>t <sub>setup</sub> | Hold<br>t <sub>hold</sub> | Setup<br>t <sub>setup</sub> | Hold<br>t <sub>hold</sub> | Setup<br>t <sub>setup</sub> | Hold<br>t <sub>hold</sub> |    |

| 1              | 0.10                        | 1.10                      | 1.10                        | 2.10                      | 4.90                        | 5.90                      | ns |

| 2              | -0.15                       | 1.45                      | 0.85                        | 2.45                      | 4.65                        | 6.25                      | ns |

| 3              | -0.40                       | 1.10                      | 1.10                        | 2.10                      | 4.90                        | 5.90                      | ns |

| 4              | -0.90                       | 2.45                      | 0.10                        | 3.45                      | 3.90                        | 7.25                      | ns |

| 5              | -1.10                       | 2.70                      | -0.10                       | 3.70                      | 3.70                        | 7.50                      | ns |

| 6              | -1.40                       | 3.10                      | -0.40                       | 4.10                      | 3.40                        | 7.90                      | ns |

| 7              | -1.80                       | 3.55                      | -0.80                       | 4.55                      | 3.00                        | 8.35                      | ns |

| 8              | -1.95                       | 3.75                      | -0.95                       | 4.75                      | 2.85                        | 8.55                      | ns |

Table 3: Synchronous Clock Timing

Delay Class can be selected in a dialog **Settings**  $\rightarrow$  **Clock Source**. All inputs must be set up for the same Delay Class.

## 4.2 Input pins

The term **input pin** refers to physical input of OMEGA Logic Analyzer. The logic analyzer use fixed input threshold levels compatible with TTL or 5V / 3.3V CMOS. If a particular input is not required by user, but its value differs from logic 0, OMEGA can disable some of the unused inputs to save amount of required memory for data acquisition. If the unused pins are in logic 0 (weak internal pull-down will guarantee this), the amount of saved memory is negligible.

The number and placement of used input pins can be selected in *Inputs Dialog*. The dialog can be opened using **Settings**  $\rightarrow$  **Inputs** menu or using *I* hotkey.

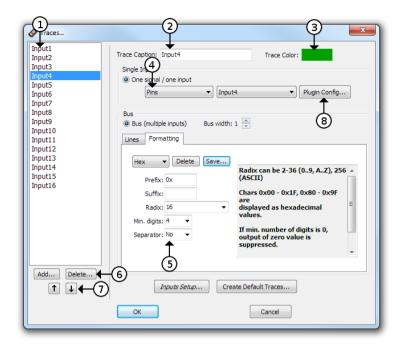

## 4.3 Traces

The term **trace** refers to visualization of acquired data. A trace can be composed of several inputs as well, otherwise a single input may be used in multiple traces, e.g. it is possible to visualize several inputs as a bus while still having the possibility to display individual signals.

Traces are defined in *Traces dialog*. The dialog can be opened by double-clicking a name of each trace in the main viewer window, using **Settings**  $\rightarrow$  **Traces** menu or using **Ctrl+T** hotkey.

#### **Traces Dialog**

1 List of traces

The selected trace is being edited.

#### 2 Trace caption

Trace caption can have arbitrary name. Common negation characters in the expression are treaded as a negation.

3 Trace color

The color is mixed with color for logic 0 and logic 1.

4 Input selector

When the selector selects a decoder, it can be directly configured via *Plugin Config...* button (8).

#### 5 Bus number setup

Any textual *prefix* and *suffix* can be selected, *radix* can be in range of 2 to 36.

6 Add and Delete Trace buttons Click the button to add a new trace or delete one.

#### 7 Trace move buttons

Click the button to move the trace up and down. The shortcut to use the buttons is  $\mathbf{Shift} + 1$  and  $\mathbf{Shift} + 1$ .

#### 8 Plugin Config Dialog

When a decoder is selected as source of the data, the configuration of the decoder can be invoked by pressing the *Plugin Config Dialog* button.

If a trace is defined as a bus, the value on the bus will be displayed according to configurable formatting. Radix from 2 to 36 can be used to format the value as a number using alphabetical characters A-Z for digits 10-35. There is also special formatting option for displaying data as ASCII characters; values which do not represent a printable character in selected set are shown as hexadecimal numbers. The output may be prefixed by a text, suffixed by a text or padded with zeros from the left to given particular width and likewise digit grouping can be used.

## 4.4 Trigger Settings

Trigger options are defined in the *Trigger settings dialog*. The dialog can be invoked from menu by **Settings**  $\rightarrow$  **Trigger Setup** or using a **T** hotkey.

Availability of certain trigger settings depends on clock settings. For higher sample rates, only basic trigger on an edge of a selected input signal is available. In the other modes either a pin trigger or an advanced trigger can be used. The advanced trigger allows user to set up precise specification of a trigger condition.

### 4.4.1 Basic Trigger Settings

| Trigge                   | er O  | ptio   | ns           |      |              |      |       |          |      |       |     |      |       |       |      | ×                      |

|--------------------------|-------|--------|--------------|------|--------------|------|-------|----------|------|-------|-----|------|-------|-------|------|------------------------|

| Pin Tr                   | rigge | r Se   | tting        | s    | Adva         | ance | d Tri | igge     | r Se | tting | s   | Othe | er Se | tting | gs   | OMEGA Real-Time Mode   |

| <b>V</b> U               | lse S | Simple | e Pin        | Trig | gger         | Sett | tings |          |      |       |     |      |       |       |      |                        |

| Pin                      | Trig  | ger B  | Even         | t Se | etting       | ,    |       |          |      |       |     |      |       |       |      |                        |

| Trig                     | ger   | word   | is:          |      |              |      |       |          |      |       |     |      |       |       |      |                        |

| 1                        | 2     | 3      | 4            | 5    | 6            | 7    | 8     | 9        | 10   | 11    | 12  | 13   | 14    | 15    | 16   | _                      |

|                          |       | •      | •            | •    | •            | •    | •     |          |      |       |     |      |       |       |      | ×                      |

|                          | 0     |        |              |      |              |      |       |          | 0    |       | 0   | 0    |       |       | 0    |                        |

|                          | ╞     | ╞      |              |      |              |      |       |          |      |       |     | -    |       |       | -    | 1<br>Dision adap       |

| ↑<br>↓                   | ╞     | ╞      | -            |      |              |      |       | <b>Τ</b> |      | -     | -   | -    | ╞     |       | -    | Rising edge            |

|                          |       |        | ļ            | ļ    |              | ļ    | ļ     | <b>v</b> | ļ    | ļ     | ļ   | ļ    |       | ļ     | ļ    | Falling edge           |

|                          |       |        | ent v<br>red |      |              | ure  | whe   | en a     | ny : | sele  | cte | d ch | ang   | e ta  | ikes | place while other pins |

|                          |       |        |              |      |              |      |       |          |      |       |     |      |       |       |      |                        |

| Trig                     | ger ( | occu   | res:         |      |              |      |       |          |      |       |     |      |       |       |      |                        |

| -                        |       |        | / Eve        |      |              |      |       |          |      |       |     |      |       |       |      |                        |

|                          |       |        |              |      | fn-t<br>occu |      |       | ance     | 2    |       |     |      |       |       |      |                        |

| _                        |       |        |              |      |              | - F  |       |          |      |       |     |      |       |       |      |                        |

| Number of occurrances: 1 |       |        |              |      |              |      |       |          |      |       |     |      |       |       |      |                        |

|                          |       |        |              |      |              |      |       |          |      |       |     |      |       |       |      |                        |

|                          |       |        |              |      |              |      |       | 214      | _    |       |     | ſ    |       |       |      | 1                      |

|                          |       |        |              |      |              |      | (     | Ж        |      | )     |     |      | C     | ance  | 21   |                        |

Fig. 10: Basic Trigger Settings

Basic trigger settings define a trigger event as a combination of desired levels and edges on input pins.

**Note:** Although setting the edge detector on more than one input pin lacks a little sense, it is possible to set the edge detector on up to two input pins. The acquisition is then triggered only when an edge is detected within one clock period of the detector logic, which is 10 ns. This can be somehow useful for race condition hunting, but the probability of the detection is disputable.

The trigger can occur immediately (occurs as soon as the

defined combination turns up) or delayed by a counter.

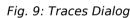

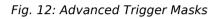

### 4.4.2 Advanced Trigger Settings

Advanced trigger settings define the trigger event by a set of boolean expressions in combination with an advanced event and delay counter.

| 1 r Options                                                                        |

|------------------------------------------------------------------------------------|

| Pin Trigger Settings Advanced Trigger Settings Other Settings OMEGA Real-Time Mode |

| Use Advanced Trigger Settings                                                      |

| Trigger Event izzhen                                                               |

| (†(!Input1   Input2) AND (Input3 & !Input4))                                       |

| occurres after at least one occurrance of  (1,1/input9)                            |

|                                                                                    |

| 5 6                                                                                |

| Trigger Occurres                                                                   |

| On every Event                                                                     |

| Upon beginning of n-th Event     Don end of n-th Event                             |

| Number of Events: 1                                                                |

| © Event length (Time between begin and (8) 9 10                                    |

| Time distance of Events (Time between two beginnings)                              |

| Gap between Events (Time between end and begin of next event)                      |

| 0.9984 ms ▼ ≤ length ≤ 49.99936 ms ▼                                               |

| When no Event occurres for 0 ms -                                                  |

|                                                                                    |

|                                                                                    |

|                                                                                    |

| OK                                                                                 |

Fig. 11: Advanced Trigger Settings

#### Advanced Trigger Dialog Overview

- 1 Advanced Trigger Selector

- 2 Trigger Mask

The mask made of any number of inputs can be selected. The inputs in the mask can be either *ANDed*, *ORed*, *NANDed* or *NORed*, but not their combination.

- **3** Boolean Function between Masks There can be any boolean function of list AND, NAND, OR, NOR, XOR, XNOR.

- 4 Adder of new Functions and Masks A new function and a mask can be added by clicking the adder mark.

- **5 Inversion or Edge** *Detector* Nothing, inversion or any edge detectors can be set up here. The detector include *rising edge, falling edge* and *any edge*.

- 6 Precondition toggle button

A precondition can be enabled and disabled by clicking on the *precondition* button. The trigger is then detected only when a boolean condition is matched after at least one occurrence of the precondition.

7 Advanced event and delay Counter

The event and delay counter enables a time and count related condition.

8 Lower than / Higher than / Constraints toggle button

By clicking the *length* button the condition will toggle between a *Lower than / Higher Than / Constraints* condition.

9 Value with prescaler

The value of the counter. Due to a prescaler, the value may be rounded to nearest value achievable with the prescaler.

#### 10 Unit selector

**Note:** There are three *masks* available for the *condition* and *precondition* in total. The *condition* must use at least one, therefore at most two *masks* are available for the *precondition*.

#### Mask selection

#### 1 Edge and inversion selector

- 2 Input or trace Term The term can also have negation and in case of busses constant comparison<sup>2</sup>.

- 3 Mask function selector The selector can be either AND or OR.

- 4 Add new input term

- 5 Delete one term

Although this approach makes the description of very complex situations possible, accordingly it allows to define the moment to be captured precisely, there are certain limitations determined by capabilities of the hardware. If the expression is too complex to be implemented in the OMEGA Logic Analyzer hardware, an exclamation icon appears to indicate this fact.

## 4.4.3 Trigger Position within Acquisition

The *Post-Trigger Time* can be selected on the **Other Trigger Settings** tab of the **Trigger Settings** dialog. This *Post-Trigger Time* selects the amount of logic analyzer **memory** which can be used after the acquisition was triggered. The rest of the memory is used as *Pre*- *Trigger Time*. If the trigger was detected before the whole *Pre-Trigger Time* memory was wasted, the remaining memory will not be used, even for the *Post-Trigger* acquisition. If the amount of the memory used is greater than the *Pre-Trigger* memory amount, the very beginning of the acquisition is dropped.

The *Post-Trigger Time* setting can be set from range of 1-99% with resolution of 1%. The accuracy of the setting is within  $\pm 1\%$ .

### 4.4.4 External Triggering

The OMEGA Logic Analyzer comes with *Trigger In* and *Trigger Out* pins (on the SIGCAB20 cable described as **TI** and **TO**). The *Trigger Out* can be configured as 3.3V CMOS output with negative or positive polarity or as an open collector output. The *Trigger Out* pulse length can be set to either  $1 \mu s$  or 1 ms.

The *Trigger In* input can be configured as positive or negative polarity. The function of *Power Out* can be configured on *Trigger In*.

The *Trigger In* and *Trigger Out* pins are shared with *Daisy Chain* functionality on the OMEGA Logic Analyzer.

The source of the activation of the *Trigger Out* pin can be selected from variety of sources:

- By external *Trigger In*.

- By trigger by trigger condition.

- By trigger by GO button.

- By trigger in PC software.

- During acquisition.

- During acquisition after it has been triggered.

|                                              | Min. | Тур. | Max. |    |

|----------------------------------------------|------|------|------|----|

| $V_{L}$ input low voltage                    |      |      | 0.8  | V  |

| V <sub>IH</sub> input high voltage           | 2.0  |      |      | V  |

| V <sub>IN</sub> absolute rating, trigger I/O | -0.3 |      | 3.6  | V  |

| V <sub>PO</sub> power output on Trigger In   | 2.0  | 2.4  | 3.3  | V  |

| I <sub>PO</sub> power output on Trigger In   |      |      | 100  | mA |

Table 4: Electrical Specification on the Trigger In/Out Pin

**Warning:** The absolute maximum voltage on the *Trigger In* and *Trigger Out* pins is 3.6V.

### 4.4.5 Other Trigger Settings

During normal acquisition, the acquisition is triggered by first occurrence of the trigger from beginning of the acquisition. If any successive triggers are detected, they are ignored by the *Post-Trigger* acquisition termination logic, but the *Trigger LED* can be configured to either blink on every detected trigger or only on the first trigger launching the acquisition.

### 4.4.6 Amount of triggers

When using *OMEGA Real-Time Mode*, the trigger is being detected and stored during whole acquisition, not only for the first time to trigger the acquisition.

|        | Settings<br>300 ms | 1 1 | Help<br>'  <br>) ms | <br>300 ms | 1 |   |

|--------|--------------------|-----|---------------------|------------|---|---|

| Input1 |                    |     |                     |            |   | = |

| Input2 |                    |     |                     |            |   |   |

| Input3 |                    |     |                     |            |   |   |

| Input4 |                    |     |                     |            |   |   |

| (      |                    | -   | -                   | III        |   |   |

Fig. 13: Time scale around trigger

The time scale zero time can be set to:

- The beginning of the acquisition.

- The first trigger.

- The last trigger.

The viewer can be set to display:

- Only the first trigger.

- Only the last trigger.

- Every trigger.

| Note: | Setting the trigger as an event which is very often<br>(e.g. rise edge of a communication clock) is <b>highly</b><br><b>discouraged</b> in the <i>real-time mode</i> because the<br>trigger is stored in the FIFO and consumes significant<br>amount of the buffer. The performance of the<br>software is also reduced when displaying lot of |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | triggers.                                                                                                                                                                                                                                                                                                                                     |

#### **Trigger Filter**

The trigger filter is a filter which reduces the number of triggers to one per millisecond, but allowing bursts of up to 256 triggers. The filter should be always turned on during normal operation.

## 4.5 Working with the acquired data

## 4.5.1 Navigation and analysis

Navigation in the main viewer can be controlled by keyboard, mouse or by a combination of both.

| Action                               | Key or mouse action       |  |  |

|--------------------------------------|---------------------------|--|--|

| Viewer window sliding along the      | ← or →                    |  |  |

| time axis                            | mouse wheel               |  |  |

|                                      | Ctrl and mouse move       |  |  |

| Zoom                                 | + or -                    |  |  |

|                                      | Ctrl and mouse wheel      |  |  |

|                                      | Select by mouse drag      |  |  |

| Undo last zoom / move                | Backspace                 |  |  |

| Zoom 50× in                          | *                         |  |  |

| Zoom whole acquisition <sup>3</sup>  | /                         |  |  |

| Jump to acquisition end <sup>3</sup> | End                       |  |  |

| Jump to trigger <sup>3</sup>         | Home                      |  |  |

| Move mouse to another trace          | ↑ or ↓                    |  |  |

| Jump to next edge on selected trace  | Alt+→ or Alt+←            |  |  |

| Place bookmark                       | Ctrl+Shift+0 to 9         |  |  |

| Jump to bookmark                     | <b>Ctrl+0</b> to <b>9</b> |  |  |

| Place marker                         | Space                     |  |  |

| Count number of edges                | Q                         |  |  |

| Toggle between period and frequency  | F                         |  |  |

| Display counting options             | QQ                        |  |  |

Table 5: Mouse and Keyboard action for navigation and analysis

| 2 700 | με 2 704 με 2 708 με 2 712 με | 2716 μs 27                                                |

|-------|-------------------------------|-----------------------------------------------------------|

|       |                               | 16 rising edges<br>2 713 865 ns<br>13 240 ns<br>2 648 CLK |

Fig. 14: Counting edges in an acquisition

**Note:** Several functionality of the software is coded in plugins. All described functionality is within plugins distributed together with the software. By disabling or replacing the plugins, the functionality will differ.

### 4.5.2 UART Protocol Decoder

This decoder decodes captured UART signal and displays ASCII characters, decimal or hexadecimal values.

| UART Settings                                     |                     |

|---------------------------------------------------|---------------------|

|                                                   |                     |

| UART #1 UART #2                                   |                     |

| UART #1                                           | Add New Decoder     |

| Source: RA4                                       | Delete This Decoder |

| ✓ Line is inverted (<0.8V = log.1; >2.0V = log.0) |                     |

| Start Bit is inverted (log.1)                     |                     |

| Stop Bit is inverted (log.0)                      |                     |

| Display Start Bits                                |                     |

| V Display Stop Bits                               |                     |

| Display Parity Bit                                |                     |

| ✓ Display Bit Frames                              |                     |

|                                                   |                     |

| Start bits: 1 💌                                   |                     |

| Data bits: 8 💌                                    |                     |

| Stop bits: 1                                      |                     |

| Parity: None                                      |                     |

| Speed: 2400                                       |                     |

| Display: hexadecimal 💌                            |                     |

| <u> </u>                                          | Cancel              |

Fig. 15: UART Decoder

Several options can be set up:

#### Input

The input pin.

#### **Line Polarity**

The polarity of the line. This is useful when using direct connection of voltage limited RS-232 (be aware of maximum ratings on OMEGA pins).

#### **Start Bit Inversion**

The polarity of the start bit and idle bus logic level.

#### **Stop Bit Inversion**

The polarity of the stop bit.

#### **Bit Frames Visibility**

This option enables display of bit frames.

#### **Data Bits**

The number of start bits can be configured from  ${\bf 1}$  to  ${\bf 16}.$

#### **Start Bits**

The number of start bits can be configured to **1** or **2**.

#### **Stop Bits**

The number of stop bits can be configured to **0**, **1** or **2**.

#### Parity

The decoder can check parity bit. The parity can be set to **None**, **Even**, **Odd**, **Mark**, **Space**.

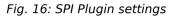

### 4.5.3 SPI Bus Decoder

This decoder decodes captured SPI signal and displays it as hexadecimal values. For correct function it is necessary to set up an appropriate data input, a clock input and an input that trigger counting of bits in a byte.

| SPI Settings<br>SPI #1 |            |                          |

|------------------------|------------|--------------------------|

| SPI Bus #1             |            | Add New Decoder          |

| DATA Source:           | Input1     | ✓ Delete This Decoder    |

| CLK Source:            | Input2     | 🔽 🗹 DATA on rising edge  |

| SYNC Source:           | Input3     | 🖌 🗔 Start on rising edge |

| 📃 DATA are M           | ISB        |                          |

|                        | <u>0</u> K |                          |

Several options can be set up:

#### Input pins

Three inputs pins for *Data*, *Clock* and *Synchronization* (i.e. -CS).

#### **Clock polarity**

Data on *rising* or *falling* edge of Clock.

#### Data Sequence

The data sequence MSB first or LSB first.

#### Sync polarity

The edge on which is started decoding can be set to **rising** or **falling** edge.

#### Field bit length

Allows user to define length of each field in order how they come after start of the frame (SYNC). One or more last fields can be closed in brackets indicating repetition (Ex.: 12,(8,16)).

### 4.5.4 I2C Bus decoder

This decoder decodes captured I2C signal and displays start bits, stop bits, addresses, acknowledge bits and data in hexadecimal values.

| 12C Bus Sett | ings                     |          |                     |

|--------------|--------------------------|----------|---------------------|

| 12C #1       |                          |          |                     |

| 12C Bus #1   |                          |          | Add New Decoder     |

| SCL Source:: | Input1                   | <b>~</b> | Delete This Decoder |

| SDA Source:  | Input2                   | <b>~</b> |                     |

| 🗹 Display 12 | C address byte 7bit long |          |                     |

|              | <u>0</u> K               |          | <u>C</u> ancel      |

Fig. 17: I2C Plugin settings

Several options can be set up:

#### Input pins

Two input pins for **SDA** and **SCL** signal.

#### Display address 7bit long

There are two possibilities how to display I2C address: with or without the LSB displayed (e.g. A0/A1 device address is displayed as A0W/A1R in first case or 50W/50R in the latter).

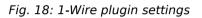

### 4.5.5 1-Wire Bus decoder

This decoder decodes captured 1-Wire signal. It shows reset pulses (R), presence pulses (P) and data in hexadecimal format.

| 1-Wire Settings |                |

|-----------------|----------------|

| 1-Wire #1       |                |

| Source:         |                |

| Input1          | ∼ Add Decoder  |

| Overdrive speed | Delete Decoder |

| OK              | Cancel         |

Several options can be set up:

#### Source

Selects an input pin containing the signal to be decoded.

#### **Overdrive speed**

By setting this option the overdrive speed is selected, when not set it is supposed that there is normal communication speed on the 1-Wire bus.

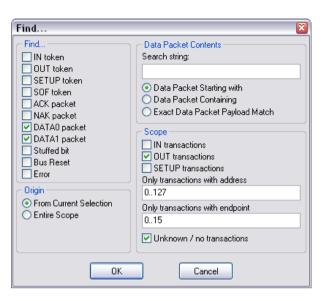

### 4.5.6 USB 1.1 Analyzer Plugin

The USB 1.1 Analyzer decodes captured signals as USB 1.1 signals. Reading of the USB specification is highly recommended before using the USB decoder.

First of all a new decoder must be added in the **Settings**  $\rightarrow$  **Plugin Settings**  $\rightarrow$  **USB Plugin Configurations** menu using the *Add New Decoder* button and the captured signals to be decoded must be chosen. After the OK button is pressed, a decoded data window is opened. The data decoding is triggered by menu **Other**  $\rightarrow$  **Decode Now!** or by the **F9** key. The communication is decoded automatically after the data have been completely downloaded from the analyzer if the field

"Decode protocol automatically upon data download" is checked in the settings.

After decoding, the communication is displayed in a tree structure where all the packets are listed. The decoded packets can be itemized to the bits level. After clicking the decoded packet or some of its part, the appropriate part of the captured traces is highlighted. After right mouse button clicking a **Zoom** function from the local menu can be used. The **Search**  $\rightarrow$  **Find...** function of the main menu provides various possibilities how to search in the decoded data.

**Note:** A dedicated hardware probe for easy connection of the USB signals to the logic analyzer can be purchased optionally. It is equipped with two USB A connectors (plug and receptacle) and pins for the logic analyzer connection. The logic analyzer can be connected either directly to the USB signals or to the buffered USB signals. On the USB cable there must be found a suitable position for the probe, where the captured signals are the best quality.

#### Installation

The USB decoder has been drawn up as one of the plugins and it is a part of the installation package and so there is no need to install it separately.

#### What to measure

With USB decoder USB 1.5 Mbps (Low-Speed) and 12 Mbps (Full-Speed) data communication captured by the OMEGA Logic Analyzer can be analyzed. The logic analyzer is not capable of capturing higher data rates (High-Speed, Super-Speed).

#### Measure tool attachment

Although the USB data communication is partly differential. GND and both USB data signals (DATA+. DATA-) must be connected to the OMEGA Logic Analyzer. OMEGA samples that signal with enough accuracy as a common TTL signal. Due to NRZI coding, which is used by USB. it is not needed to distinguish between DATA+ and DATA-, they are interchangeable. Unfortunately, there are some states on the USB using single-ended signaling (Bus Reset and End-Of-Packet). This is the reason why the connecting of both signals DATA+ and DATA- is required. Connecting of single signal DATA line is not enough. The data rate is chosen by swapping the data lines. Behind the USB hub on the lines to a Low-Speed (1.5 Mbps) device there is only Low-Speed communication, whereas on the lines to Full-Speed (12 Mpbs) device there are both Low-Speed and Full-Speed communication observable. The 480 Mbps communication is called High-Speed and OMEGA is not capable to measure that.

The USBprobe includes two 74AHCT125 TTL gates and two USB connectors of type A and B wired so that it acts as a USB extension. The OMEGA Logic Analyzer can be connected before or beyond the buffer, it depends on an application – better to try. Generally, best results are reached with USBprobe connected directly to a USB hub and the shorter USB cable, the better. Likewise it is important to shorten the way between USBprobe and OMEGA.

On *USBprobe* there are 5V directly accessible from PC (through a 800mA irreversible fuse) – avoid a shortage! \*It is highly inadvisable to connect USBprobe directly to PC ports\*. We suggest using a USB hub with an external power source and connecting *USBprobe* directly into the hub.

#### Measuring

The USB data signals (DATA+, DATA-) can be connected to any two inputs and the other inputs can be utilized for measuring of any other signals (e.g. for measuring of another USB communication). It is possible to analyze more than one USB communication.

#### Processing

When signals have been captured (= the acquisition has been done) they have to be decoded. It can take tens of seconds depending on amount of the captured data. Decoding is done automatically, immediately when the data have been captured, if it is enabled in the USB analyzer settings dialog. Or it can be started in the menu by choosing **Decode**  $\rightarrow$  **Decode Now!** or hitting **F9**.

When decoding have finished there is a list of measured USB events in the events window (which is simultaneously the main window).

#### Viewing

After the decoding have finished the list of measured USB events is in the events window.

To decrease the number of events in the event window a configurable filter can be applied so that only requested events are displayed. For that option open the menu **Settings**  $\rightarrow$  **Filter Settings**. One or more USB addresses can be marked. The formatting can contain a single address or address ranges (e.g. 0, 5..7) within range of 0 to 127 (USB uses 7bit wide address range). The same principle applies to endpoints within range of 0 to 15 (the endpoint direction – bit 7 - does not matter).

The *address zero* is dedicated for the device without any address yet. The *zero endpoint* is special *control endpoint*, which each device must implement. It is the only endpoint with bi-directional transactions.

Due to the fact that the USB specification does not allow devices to send data by their own, the major part of the traffic is occupied by a master device (PC) asking slave devices whether they have some data to be transferred.

Therefore it can be useful to mask out the frames without any useful data (terminated by a *NAK* token). For doing that, as well as for masking frames which are not designated for any particular device (e.g. a *Start-Of-Frame* token, *Bus Reset*), use the menu **Settings**  $\rightarrow$  **Filter Settings**.

On the highest level of the decoded data tree there is a possibility to display or hide transactions ended by a *NAK* token or a *ACK* token, for that option use the right mouse button and control the filter from the local menu.

| USB Filter Settings                              | ×                 |

|--------------------------------------------------|-------------------|

| - Shown packets                                  |                   |

| Show packets for addresses                       | 0127 ALL          |

| and endpoints                                    | 015 ALL           |

| Show addressless and end Hide NAKed transactions | pointless packets |

| ОК                                               | Cancel            |

Fig. 19: USB Filter settings

Another way how to pop-up the dialog Settings  $\rightarrow$  Filter Settings menu is to click on the title of Addr or Endpoint column.

| Search Decode Settings Help |         |      |      |                |       |   |

|-----------------------------|---------|------|------|----------------|-------|---|

| Time                        | Length  | Addr | Endp | Record         | Notes |   |

| 4 590 246 093ns             | 37.9µs  | 2    | 81   | IN transaction | NAK   | 2 |

| 4 594 245 903ns             | 37.8µs  | 2    | 82   | IN transaction | NAK   |   |

| 4 598 245 713ns             | 37.8µs  | 2    | 81   | IN transaction | NAK   |   |

| 4 602 245 523ns             | 37.9µs  | 2    | 82   | IN transaction | NAK   |   |

| 4 606 245 298ns             | 107.5µs | 2    | 81   | IN transaction | ACK   |   |

| 4 610 245 108ns             | 37.8µs  | 2    | 82   | IN transaction | NAK   |   |

| 4 614 244 883ns             | 37.9µs  | 2    | 81   | IN transaction | NAK   |   |

| 4 618 244 723ns             | 37.8µs  | 2    | 82   | IN transaction | NAK   |   |

| 4 622 244 533ns             | 37.9µs  | 2    | 81   | IN transaction | NAK   |   |

| 4 626 244 308ns             | 37.9µs  | 2    | 82   | IN transaction | NAK   |   |

| 4 630 244 118ns             | 37.8µs  | 2    | 81   | IN transaction | NAK   |   |

| 4 634 243 893ns             | 37.8µs  | 2    | 82   | IN transaction | NAK   | C |

| 4 638 243 738ns             | 37.8µs  | 2    | 81   | IN transaction | NAK   |   |

| 4 642 243 513ns             | 37.8µs  | 2    | 82   | IN transaction | NAK   |   |

| earch <u>D</u> ecode S | <u>e</u> ttings <u>H</u> el | p    |         |                                    |                                    |   |

|------------------------|-----------------------------|------|---------|------------------------------------|------------------------------------|---|

| Time                   | Length                      | Addr | Endp    | Record                             | Notes                              |   |

| 1 960 223 868ns        | 4.4ms                       | 2    | Control | Control transfer                   | Get unknown tyre (34) Descriptor 0 | 1 |

| 2 990 783 858ns        | 337.9µs                     | 2    | Control | Control transfer                   | Class Specific Aequest 9           |   |

| 4 014 274 803ns        | 106.8µs                     | 2    | 81      | IN transaction                     | ACK                                |   |

| 4 070 271 993ns        | 107.5µs                     | 2    | 81      | IN transaction                     | ACK                                |   |

| 4 222 264 438ns        | 106.8µs                     | 2    | 81      | <ul> <li>IN transaction</li> </ul> | ACK                                |   |

| 4 294 260 863ns        | 107.6µs                     | 2    | 81      | <ul> <li>IN transaction</li> </ul> | ACK                                |   |

| 4 542 248 523ns        | 107.6µs                     | 2    | 81      |                                    | ACK                                |   |

| 4 606 245 298ns        | 107.5µs                     | 2    | 81      | IN transaction                     | ACK                                |   |

| 4 678 241 723ns        | 107.5µs                     | 2    | 81      | IN transaction                     | ACK                                |   |

| 4 742 238 533ns        | 107.6µs                     | 2    | 81      | IN transaction                     | ACK                                |   |

| 4 854 232 953ns        | 106.8µs                     | 2    | 81      | <ul> <li>IN transaction</li> </ul> | ACK                                |   |

| 4 918 229 763ns        | 107.4µs                     | 2    | 81      | IN transaction                     | ACK                                |   |

| 4 982 226 573ns        | 106.9µs                     | 2    | 81      | IN transaction                     | ACK                                | 1 |

| 5 062 222 548ns        | 107.6µs                     | 2    | 81      | IN transaction                     | ACK                                |   |

Fig. 20: Window with hidden transactions which are ended with NAK

#### Searching

For searching for a specific type of packet or event (*Bus Reset*, any error, *Stuffed Bit*) open the **Search**  $\rightarrow$  **Find...** menu or hit **Ctrl+F** and then for another occurrence hit the **F3** key.

Fig. 21: Searching Window

Fig. 22: DATA0 Packet Highlighted

If data packets (DATA0, DATA1) are being searched, searching can be limited to particular endpoint, device address or by a hexadecimal string.

## Linking the events window with the analyzer window

When a particular USB event has been chosen the real place of the occurrence is highlighted in the analyzer window. The place can be also zoomed in by hitting the right mouse button and then choosing **Zoom**. Hitting the right mouse button in the analyzer window and then choosing **Lookup** in USB Communication highlights position in the events window.

## Gathering of related communication into trees

In the basic USB decoder settings, related consecutive events are gathered into a tree (e.g. whole *Control Transfer*). This behavior leads to potential ambiguity in the order of USB events. In this case *Flat Decoding* can be chosen in the *Settings*  $\rightarrow$  *Settings...* menu. It disables gathering of USB events so they are sorted top-down strictly by the time.

## 4.6 Auxiliary functions

The OMEGA Logic Analyzer have some useful auxiliary functions. This functions are controlled all at once using a gateway dialog **Settings**  $\rightarrow$  **Utilities Setup...**.

Fig. 23: Dialog Utilities Setup

#### Setup Logic Analyzer

This opens *Clock Source* dialog and allows setup operation mode and number of input pins.

#### **Setup Inputs**

This opens *Inputs Setup* dialog where unused inputs can be selected.

#### **Setup Insider**

This opens *Insider Setup Wizard*. See chapter Insider.

#### **Setup Function Generator**

This opens *Function Generator Setup*. See chapter Function Generator.

#### **Frequency Measuring**

This opens *Frequency Measuring* and allows measuring of duty cycle and frequency on one pin.

### 4.6.1 Insider

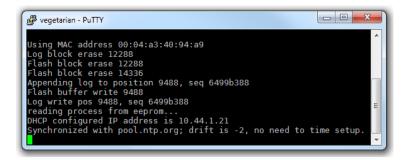

OMEGA Insider is a tool for real-time sniffing of most common busses and streaming them to a TCP/IP port. The output stream can be displayed by a common terminal program, such as PuTTY. Home page of PuTTY is https:// www.chiark.greenend.org.uk/~sgtatham/putty/.

OMEGA Insider can be set up using OMEGA Insider Wizard. The wizard can be launched from *Utilities dialog* (can be opened using **Settings**  $\rightarrow$  **Utilities Setup...** or by pressing the **U** key).

Fig. 24: OMEGA Insider Wizard

The wizard can work in one of five modes.

| Mode                                  | Bus         | Туре        | Purpose                                                                      | Example of<br>Required<br>Settings                                                                     | Pin<br>Requirements                                                   |

|---------------------------------------|-------------|-------------|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| I <sup>2</sup> C Bus Slave            | ι²c         | Debug texts | Log texts<br>written to<br>OMEGA as I <sup>2</sup> C<br>bus slave<br>device  | OMEGA I <sup>2</sup> C<br>Bus Slave<br>Address<br>I <sup>2</sup> C Bus Speed<br>(100 kHz /<br>400 kHz) | Input 1 (SDA),<br>Input 2 (SCL),<br>Input 9, Inputs<br>10-16 unusable |

| I <sup>2</sup> C Bus Logger           | i²c         | Bus logger  | Log all bus<br>activity<br>including<br>addresses,<br>data, ACKs and<br>NAKs | I <sup>2</sup> C Bus Speed<br>(100 kHz /<br>400 kHz)                                                   | Any two inputs                                                        |

| SPI Bus Logger                        | SPI         | Bus logger  | Log all bus<br>activity using<br>single -CS wire.                            | Single (DATA)<br>or dual data<br>(MISO, MOSI)<br>lines, CS<br>polarity, SPI Bus<br>mode (0/1/2/3)      | Any three or<br>four inputs.                                          |

| Universal<br>Synchronous<br>Receiver  | Synchronous | Debug texts | Log texts sent<br>using DATA/<br>CLK wires.                                  | Optional byte<br>synchronization<br>using third wire<br>or timer.                                      | Any two or<br>three inputs.                                           |

| Universal<br>Asynchronous<br>Receiver | UART        | Debug texts | Log texts sent<br>using TXD wire.                                            | Baud rate, start<br>bit inversion.                                                                     | Any single<br>input.                                                  |

*Table 6: OMEGA Insider Modes*

The debugging or logging texts are available on a selected TCP/IP port. Connect to the port with your favorite terminal application.

Fig. 25: Opening Insider Connection in PuTTY

The picture above shows the basic options required to open the connection in the PuTTY terminal application. For connecting within one PC, as host use "*localhost*". The host can be, if required, filled with any other host reachable on the network.

| رچی<br>SD |      |    |     | Pul |     |   |    |    |    |    |    |     |     |     |    |    |     |   |     |   |     |    |     |   |      |   | C   |   |     |   |     |   |

|-----------|------|----|-----|-----|-----|---|----|----|----|----|----|-----|-----|-----|----|----|-----|---|-----|---|-----|----|-----|---|------|---|-----|---|-----|---|-----|---|

|           | ST   | 6F | W A | Θ   | 0 A | S | Γб | FF | Α  | 84 | A  | 22  | 2 A | 13  | A  | 38 | 3 A | 1 | 3 A | 1 | 1 A | 14 | 4 N |   |      |   |     |   |     |   |     | - |

| ST        | 57W  | A  | 50  | Α   | ST  | 5 | 7R | А  | AO | А  | 19 | А   | 64  | Α   | 54 |    | SP  |   |     |   |     |    |     |   |      |   |     |   |     |   |     | Ξ |

| ST        | 57W  | A  | F2  | Α   | ST  | 5 | 7R | А  | 00 | А  | 04 | А   | A3  | Α   | 40 | А  | 94  | A | A9  |   |     |    |     |   |      |   |     |   |     |   |     | Ц |

| ST        | 57W  | A  | 60  | Α   | ST  | 5 | 7R | А  | 00 | А  | 00 | А   | 00  | А   | 00 | А  | 00  | Α | 00  | Α | 00  | Α  | 00  | Α | 00   | А | 00  | А | 00  | А | 00  |   |

|           |      |    |     |     |     |   |    |    |    |    |    |     |     |     |    |    |     |   |     |   |     |    |     |   |      |   |     |   |     |   |     |   |

| ST        | 57W  | A  | 70  | Α   | ST  | 5 | 7R | А  | 63 |    |    |     |     |     |    |    |     |   |     |   |     |    |     |   |      |   |     |   |     |   |     |   |

| ST        | 57W  | A  | 59  | Α   | ST  | 5 | 7R | А  | B3 |    |    |     |     |     |    |    |     |   |     |   |     |    |     |   |      |   |     |   |     |   |     |   |

| ST        | 6FW  | A  | 20  | Α   | ST  | 6 | FR | А  | 01 | Α  | 00 | Α   | 00  | Α   | 00 | Α  | 00  | Α | 00  | Α | 00  | Α  | 00  | Α | ΘB   | Α | 00  | Α | 00  | Α | 00  |   |

| Α         | AC   | Α  | 15  | А   | 1A  | A | 90 | А  | 00 | Α  | 00 | Α   | 00  | Α   | 00 | Α  | 00  | Α | 00  | Α | 00  | Α  | 00  | Α | 00   | Α | 00  | Α | 00  | Α | 00  |   |

| Α         | 00   | Α  | 00  | Α   | 87  | A | ٩F |    |    |    |    |     |     |     |    |    |     |   |     |   |     |    |     |   |      |   |     |   |     |   |     |   |

| ST        | 57W  | A  | 00  | Α   | ST  | 5 | 7R | А  | FF | Α  | FF | Α   | FF  |     | FF |    | EE  | Α | EE  | Α | EE  | Α  | EE  | Α | 05   | Α | 00  | Α | 2D  | Α | 00  |   |

| Α         | 09   | Α  | 00  | А   | 14  | A | 90 | А  | 00 | Α  | 00 | Α   | 00  |     | 00 |    | 00  | Α | 00  | Α | 00  | Α  | 00  | Α | 00   | Α | 00  | Α | 00  | Α | 00  |   |

| Α         | 00   | Α  | 90  | A   | 00  | A | 90 | А  | 00 | Α  | 00 |     | 00  |     | 00 | Α  | 00  | Α | 00  | Α | 00  | Α  | 00  | Α | 00   | Α | 00  | Α | 00  | Α | 00  |   |

|           | 00   | Α  | 90  | A   | 00  | A | 90 | А  | 00 | Α  | 00 |     | 00  | А   | 00 | Α  | 00  | Α | 00  | Α | 00  | Α  | 00  | Α | 00   |   | 00  | Α | 00  | Α | 00  |   |

| Α         | 00   | Α  | 90  | A   | 00  | A | 90 | А  | FF | Α  | FF |     | FF  | А   | FF | Α  | FF  | A | FF  | A | FF  | Α  | FF  | Α | 00   | Α | 00  | Α | 00  | Α | 00  |   |

| Α         | 00   | Α  | 90  | A   | 00  | A | 90 |    |    |    |    |     |     |     |    |    |     |   |     |   |     |    |     |   |      |   |     |   |     |   |     |   |

| ST        | 57W  | A  | 68  | Α   | ST  | 5 | 7R | А  | 05 | А  | 00 | А   | 2D  |     |    |    |     |   |     |   |     |    |     |   |      |   |     |   |     |   |     |   |

| ST        | 57W  | A  | 48  | Α   | ST  | 5 | 7R | А  | 00 |    |    |     |     |     |    |    |     |   |     |   |     |    |     |   |      |   |     |   |     |   |     |   |

| ST        | 6FW  | A  | 20  | Α   | 01  | A | 00 | 1  | 00 | A  | Θ  | ) / | 00  | Ð A | Θ  | 9  | A 0 | Θ | A 6 | Θ | A O | В  | A 0 | Θ | A 00 | Ð | A 0 | 0 | A A | С | A 1 |   |

| 5         | A 1A | A  | 00  | Α   | 00  | A | 00 | 1  | 00 | A  | Θ  | ) / | 00  | Ð A | Θ  | 9  | A 0 | Θ | A G | Θ | A 0 | Θ  | A 0 | Θ | A 00 | Ð | A 0 | 0 | A 0 | Θ | A 0 |   |

| Θ         | A 87 | A  | AF  | Α   | SP  |   |    |    |    |    |    |     |     |     |    |    |     |   |     |   |     |    |     |   |      |   |     |   |     |   |     |   |

| ST        | 6FW  | A  | 40  | Α   | 01  | A | 00 | 1  | 00 | A  | Θ  | ) / | 00  | Ð A | Θ  | 9  | A 0 | Θ | A 6 | 0 | A 0 | В  | A 0 | Θ | A 00 | Ð | A 0 | 0 | AA  | С | A 1 |   |

| 5 /       | A 1A | A  | 00  | Α   | 00  | A | 00 |    | 00 | A  | Θ  | ) / | 00  | Ð A | Θ  | 9  | A 0 | Θ | A G | Θ | A 0 | Θ  | A O | Θ | A 00 | 9 | A 0 | Θ | A 0 | Θ | A 0 | - |

#### Fig. 26: Example I2C Log in PuTTY window

In the picture there is a PuTTY output of an example logging on an  $l^2C$  bus with multiple slave devices.

| File View Setting | s License Help<br>284 700 µs 285 000 µs 285 300 µs 285 600 µs 285 900 µs 286 200 µs | 286 500 µs              |

|-------------------|-------------------------------------------------------------------------------------|-------------------------|

| Input1            |                                                                                     |                         |

| Input2            | นแบบแบบการการแบบแบบแบบการการการการการการการการการการการการการก                      | mmmmm                   |

| 12C               | S 6FW A 20 AS 6FR A 01 A 00 A 00 A 00 A 00 A 00 A 00 A 0                            | A <u>08</u> A <u>00</u> |